# **Altium Designer 25 Tutorial**

Copyright (C) Istvan Nagy, 2025 <u>www.buenos.extra.hu</u> Free to share!

## 1. Introduction

This tutorial is targeting complex high-speed digital circuit board designs with Altium Designer release 2024. There are different grades of high-speed designs from the microcontroller boards up to the server computer motherboard and data center line card designs, so the methodology here to be suitable for all, is based on the high-end and scalable down.

| Al | Itium Designer 25 Tutorial1 |                       |    |  |  |  |  |  |

|----|-----------------------------|-----------------------|----|--|--|--|--|--|

| 1. | 1. Introduction1            |                       |    |  |  |  |  |  |

| 2. | Basic                       | : PCB Design          | _1 |  |  |  |  |  |

|    | 2.1.                        | Projects and Editor   | _1 |  |  |  |  |  |

|    | 2.2.                        | SCH Library           | _1 |  |  |  |  |  |

|    | 2.3.                        | PCB Library           | _2 |  |  |  |  |  |

|    | 2.4.                        | Schematics            | _2 |  |  |  |  |  |

|    | 2.5.                        | PCB Design            | _3 |  |  |  |  |  |

|    | 2.6.                        | Design Reuse          | _4 |  |  |  |  |  |

| З. | High                        | -Speed Signal Objects | _4 |  |  |  |  |  |

| 4. | Des  | ign Rules                   | 5  |

|----|------|-----------------------------|----|

| 5. | Con  | straint Manager             | 6  |

| 6. | Inte | eractive High-Sp Route      | 8  |

| 7. | Sigr | nal Integrity               | 9  |

| 8. | Тур  | ical Examples               | 10 |

|    | 8.1. | PCIe Gen4 SERDES bus design | 10 |

|    | 8.2. | DDR4 Memory-Down design     | 10 |

|    |      |                             |    |

### 2. Basic PCB Design

#### 2.1. Projects and Editor

In a **project folder** we have multiple files. One is the main project file .PRJPCB, then we have a layout file .PCBDOC, several schematic pages in separate .SCHDOC files, library files like .SCHLIB and .PCBLIB, a folder for manufacturing "ProjectOutputs". All files open in the main window design explorer, but the menus are dependent on which file type was open. A top tab can be used to select which of the open files to edit. All drawings allow CTRL+scroll for zooming.

<u>New project</u>: file>new>project, give name, enable CM (whether we want to use constraint manager) then "create". Create new files for the project on the projects panel, by right clicking the PRJPCB and then >add new to project > schematic, or PCB or library file...

| <u>File Edit View Project Place Tools</u> | <u>R</u> eports <u>W</u> indow <u>H</u> elp |                                           |

|-------------------------------------------|---------------------------------------------|-------------------------------------------|

| Projects 🔻 🖡                              | 🗙 🔺 Home Page 🔚 [1] FPGA1.SchDoc 🔚          | [2] FPGA2.SchDoc 📃 [3] MEMORY.SchDoc 📑 bu |

| = 🔹 🍬 🗞 🔹                                 |                                             |                                           |

| Q Search                                  |                                             |                                           |

| Project Group 1.DsnWrk                    |                                             |                                           |

| buenosmemboard.PrjPcb                     | Validate PCB Project buenosmemboard.PriPcb  |                                           |

| Source Documents                          | Add New to Project                          | Schematic                                 |

| [1] FPGA1.SchDoc                          | 🛃 👍 Add Existing to Project                 | РСВ                                       |

| [3] MEMORY.SchDoc                         |                                             | PCB3D                                     |

| Libraries                                 | <u>R</u> ename                              | ActiveBOM                                 |

| 🖌 🚞 Schematic Library Docι                | Close Project Documents                     | 🙀 Draftsman Document                      |

| 🧊 buenos1.SchLib 🗋                        | Close Project                               | Schematic Library                         |

Altium also has several side **panels** for browsing and editing objects. They appear depending on file type, and whether we enabled them from the "Panels" button in the lower right corner. We can dock them to the left or right side of the screen, they can be set to stacked, static, auto hide. When they hide a tab label is shown. The projects panel shows the tree structure of our project, we can open files from there. Keep these panels always visible: Projects, PCB, Properties, List.

When <u>**right clicking</u>** in the editor on empty space, a big menu opens with lots of settings and actions, dependent on what file we are editing, what mode we are in.</u>

Most companies have managed and released <u>shared libraries</u>, but one-person companies can keep library files edited within projects. We have to add existing company libraries to be accessible by the project. Either Project>Add Existing, or on the Components Panel> > Libraries Preferences> Installed> Install> select file type and browse.

#### 2.2. SCH Library

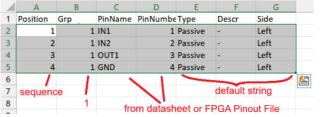

To make our own schematic symbols, we have to create/open a <u>SCHLIB file</u> on the projects panel by right clicking the PRJPCB and then >add new to project >Schematic Lib. The schlib panel opens, click Add, then enter name, select the new component it in the schlib panel. In heterogenous split components the top level is called component, the sub symbol is called a "part". They appear under the component name on the schlib panel. To add pins to the single part component or to the first part of a heterogenous

component: select component on schlib panel, then Tools > Symbol Wizard, set number of pins, then fill out the table or import from Excel. We can prepare pin tables in Excel in a matching format like below, then select data (not header), then CTRL+C to copy, then in Altium upper/left cell CTRL+V to paste. For single-part-comp or first part we press Place> Symbol, for heterogenous sub-component-parts press Place> New Part. We

can manually add more parts to a component by the III button.

On the properties panel we have to enter **parameters** like part number and value. We have to add company-specific properties, for example if we work at ACME-inc., then ACME\_PN, ACME\_DNP, MFR\_PN... We also need to add a footprint using add> footprint> browse.

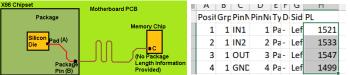

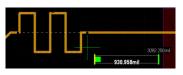

The signal length (<u>Package Length PL or PinDelay</u> A to B on diagram) within large BGA packages have to be entered for accurate length tuning later. When we are editing the schematic symbol, we have to do this separately for each sub-symbol (part). Prepare the PL data in excel (same unit as the tool, mils) for each subsymbol, sorted by pin number, select the length data only, CTRL+C to copy. In Altium select all pins in the subsymbol the drawing, but make sure the rectangle is not selected. Then open the SCHLIBlist panel, in the PinDesignator column sort, then in the Pin/PckLength column click the first item, CTRL+V to paste. Save.

#### 2.3. PCB Library

To make our own footprint symbols, we have to create/open a <u>PCBLIB file</u> on the Projects Panel> PRJPCB> rightclick >add new to project >PCB lib. The pcblib panel opens. To add a new footprint: Tools> IPC Compliant Footprint Wizard (or just the basic Footprint Wizard), fill in the parameters. Once done, we can edit it, by moving/deleting pins, Place>Pad, editing pads (click, then Properties panel edit, padstack, X/Ysize), drawing on silkscreen.

For large BGAs with **irregular** pattern, we should import from Allegro or Excel. In allegro open the reference design, export libraries, then open the footprint, reports> symbol pin report, then copy (pin number and X/Y coordinates) it into excel. We can also create this spreadsheet manually based on the datasheet in Excel. Organize the excel file to have the same columns as the Altium PCBLIBlist panel table has. In Altium, footprint library, create a package with the same number of pins using the wizard. Copy cells from Excel to Altium's PCBLIBlist XY coordinates columns. Make sure they were sorted the same way on both ends of the copy.

#### 2.4. Schematics

Every page is a separate SCHDOC file. Once we added enough SCHDOC files, in each we click Properties Panel> Sheet Size drop down to set a larger page size.

<u>Multi-page</u> schematics can be hierarchical with PORT (Place>Port) connections in the module and SHEET SYMBOL in the top level schematic. The sub-module symbol is created by: design>create sheet symbol from sheet. We can also design flat schematics with no top-level, then we have to use Place> Off Sheet.

We can place **<u>components</u>** from the "Components" panel, but first the SCHLIB file is selected on the top drop-down, then the component, doubleclick and move to desired location on schematic. Part rotation with SPACE key while moving it. Doubleclick on a part and we can see/edit properties, but don't edit here, rather in the released library. For example, have a separate library item for a 1k resistor than a 10k resistor.

A component can be do not populate DNP, to leave it out of the purchase BOM and pick&place file. Either to design for debugging (to swap a PU/PD on the prototype without trace cutting), add possible future features or product variants. We can do it in different ways depending on company; we could use a DNP property in all components and NO means in place and Yes means DNP, or overwrite the part number with "DNP", then delete these rows from the BOM manually, or we can use variants. We could have a base design (add text next near all planned DNPs as "DNP" in red), and a production variant associated with the board part number. In this variant we mark the DNPs. First we annotate refdes, then we create variants in Project>Variants>Add Variant, Close. Then in the projects panel select the variant to edit by double clicking. In the schematic on a component (sub-part-A if split part) rightclick> Part Actions> Variants> In the column named after our variant click the [...] button, select "NotFitted". All other edits should be done on the default "NoVariations" variant doubleclicked in the Projects panel.

Once components are placed, we <u>wire</u> them with . We can place power symbols with . For non-GND nets we have to place this first, then select it, then on the Properties panel select Style=Circle, add a net name like P1V0\_FPGAC, then we need to rotate it upside-down by moving and pressing TAB twice. We add net labels with Place> Net Label. We can draw buses with "signal harnesses". We can place parameter set directives with , then Add>NetClass or Rule... In older versions of Altium we had to place diffpair symbols in the schematic (Place> Directives> Diffpair), but in AD24 we should define diffpairs in the PCB CM or PCB-panel. Either way diffpair nets must be named with \_P and \_N suffixes. Nets and ports are local, Offsheet-connectors and power symbols are global on all pages. If we use off-sheet or port then we don't need net labels.

Once done, we <u>annotate</u> refdes (designator in Altium) to all components with Tools > Annotation> Force Annotate All. Then export a BOM with Reports> Bill Of Materials, and if we used variants or variant-based DNPs then we select the correct variant from the drop-down. Error checking with project>compile document. We also export a PDF schematic with File> SmartPDF.

#### 2.5. PCB Design

<u>Start:</u> Project> Add New> PCB, save. The old versions had a board wizard, that is now gone. Then we need to get a DXF file from our mechanical engineer, that contains the board outline, external connector outlines and mounting holes, and import it into a mechanical layer. File> Import> DXF, then set up scale and layer (mechanical-1). Set up View> Grids> Set Up Global Snap Grid to be coarse/accurate, View> Board Planning Mode. Then Design>Redefine Board Shape, then redraw it, then View> 2D Layout Mode, then set the grids again to 10mils for placement. Set the origin Edit>Origin>Set on the board near the lower left corner.

Once the board is set up: we have to **<u>import netlist</u>** from schematic: design> import changes from [...prjpcb] validate, execute, close. This will place all parts next to the board.

Stackup Layers: Design> Layer Stack Manager. Add layers, define their thicknesses, signal/plane type order. Also define via types like BB, microvia depths. Layers are not categorized as class/subclass like in Allegro. We use the mechanical layers for all manufacturing comments and fab notes. To enable backdrilling, click the button, select backdrills, a lower tab appears, click it, then add as many BD layer pairs as we want to use with the [+Add] button, then editing the layers on the Properties panel. BD always starts from (Top or) Bottom, and ends one layer away from our routing MNC layer. On the via types tab, we define normal via sizes, and layer pairs for microvias or BB.

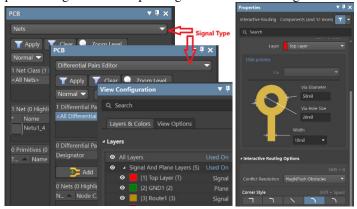

**Panels**: Enable/disable panels from the lower/right Panels button. During PCB design we use many panels, the most important one is the PCB panel, with a drop-down list on the top to select signal object type. In the PCB panel we can specify from a drop-down list what should happen when we select an object: either no effect ("Normal"), or highlight ("Dim"), or highlight and disable editing of other objects ("Mask"). It is cancelled by pressing the "Clear" button in the bottom-right corner. The View Configuration panel is needed to show/hide layers. The Properties panel changes content depending on what we are doing.

Connection Lines: View> Connections> Show/Hide...

**Layer colors** and visibility can be changed: First enable the **Panels>View Configuration** panel at the lower/left panels button. Then we can change colors and temporarily enable/disable specific layer visibility as needed, by single clicking on the eye icon **I**. In Altium everything that is on a layer (pads, vias, traces) are visible or invisible in the same time. The active layer being edited is selected on the bottom/lower labs under the PCB:

LS 🕢 🕨 📕 [1] Top Layer 📃 [2] GND1 🧧 [3] Route1 📕 [4] GND2 📕 [5]

Object Coloring: Nets can be displayed either in layer color, or net color. On the PCB panel find and select the nets, then rightclick>Change Net Color. Enable Color Override for each net using the checkbox next to its name. Set solid coloring in Tools> Preferences> PCB editor> Board Insight Color Overrides.

The new Altium supports **<u>object filtering</u>**, like Allegro. Before moving or deleting objects, we can disable others on the Properties panel> Selection Filter, to avoid affecting them.

Measure distance: Reports> Measure Distance

**<u>Find</u>** items and zoom to them: Press "J", then select component or net, then type in the refdes or net name. To display info about an object: left click, the Properties panel will display relevant data.

<u>Component placement</u> is, really just moving from the auto placed (when imported changes from SCH) area to the board design. Before placement we make inner layers hidden, so we can select components instead of planes. Click on one comp, hold and move. If it doesn't work then select the small area enveloping the component then click/move. Rotate with SPACE, or move to bottom side with "L". Move refdes as if it was a component. We can also select a few comps on the sch, if cross select mode is enabled in tools, then in the layout move them. If the refdeses are too large, then we can select one, rightlcik> Find Similar Objects> Refdes = same, OK, then on the Properties panel we change the text height. How close we can pack them is set in a constraint: CM> AlIR> Placem> CompClearance.

We can <u>place footprints</u> for floorplanning from the components panel. We can also place mounting holes and fiducials from it, although using schematic is preferred. MNT holes can also be placed as pads (Place> Pad then assign GND net).

**Design rules**: When the PRJPCB is created we have to decide whether we will be using the legacy design rules editor (DRE), or the constraints manager (CM). DRE opens from Design>Rules. CM opens from Design > Constraint Manager, and stored in constraints.xml file. We should set up at least some basic rules like clearance, width, solder mask, via style, plane connect/clr, diffpair rules before any fanout or routing. See chapters on CM/DRE.

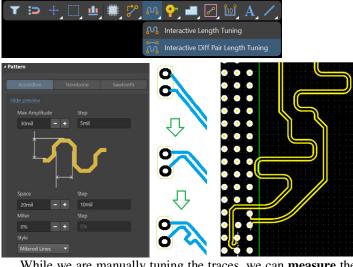

**Interactive routing** starts with the incon. Set the grids to about 1mil for routing (View>Grids). Active layer is selected by clicking the bottom tabs. Routing mode can be controlled from: tools> Preferences> PCB> Interactive Routing in advance, or from the properties panel during editing, for example push/shove. We can just click on traces to slide/edit them; we don't have to select a specific mode first like in allegro.

Add <u>Vias</u>: press "+" click while routing. Ground stitching vias can to be placed from Place>via, then assign the net name on the Properties panel. The size is set in CM> Allr> Routing> Routing Via Style (All, not net class) or DRE> Route> RoutViaSt. Altium likes to create vias with soldermask opening, but modern complex boards are made with all VIPPO (state in fab drawing notes) and complete tenting (no opening) on both sides. Cheap boards without VIPPO need complete tenting on top (especially under BGAs) and a small opening on bottom (for outgassing). So, we can select a via, rightClick> find similar > ok, then on the Properties Panel > Solder Mask Expansion = manual = tented. Or set a rule before use: CM> Allr> Mask> SolderMExp create a new rule, Object Match = "IsVia", then click checkbox for tenting. To use microvias, we have to create them in the Layer Stack Manager, based on the layer-pairs form the vendor stackup.

**<u>Fanout</u>**: Set the constraints like width, clearance, SM expansion and routing via style, as shown above. Then set up

fanout behavior with CM> Allr> Routing> Fanout Control. Then select Route> Fanout> Component, click component.

Draw Power <u>Shapes</u>: (polygon pour) on signal layers, for power delivery or VRM circuit power nets. Doubleclick to add net. Voids can be drawn with rightclick on the subtron and select Polygon Pour Cutout

**<u>Keepout</u>** shapes: place> keepout> fill, then on the Properties panel select object type to keep out (via, pad, trace...). For example, via keepout on a routing layer.

We can <u>specify areas</u> where different rules would apply locally. These areas are called "Rooms" and can be placed from the Design > Rooms > Place Rectangular Room menu. Then on the Properties panel they can be named and specify which layer to be used on. Then they can be referenced in the design rules or CM (based on room name), so the rule will only apply within the area covered by the Room. In the CM>Physical at the bottom of the table AllRooms/name we can enter new width/via constraints. This is good for example for BGA breakout neck down, or smaller via pads to implement "CLASS-3 with exception". It doesn't work for plane clearance, so use class-based clearance rules.

Power **plane layers**: Altium supports negative planes, so they need to be set in the stackup. On negative plane layers we place divider lines, enable the visibility of the layer on the ViewConf panel, then select the layer on the bottom tabs, then (Place >Line), then doubleclick an area and select net. There is also a thick outline layer to pull back from edge cuts.

Plane voids: All signal vias passing through planes will have an antipad. Altium automatically removes all non-functional pads (NFPs) on plane layers, but leaves them on signal layers. That also shrinks the antipads on the plane layers to AP= drill+2\*CL clearance rule value, while keeping them larger AP= pad+2\*CL on signal layer power shapes. Most signals are fine with tight APs around their via barrels, based only on etching clearance, but SERDES signals need enlarged pads for via-impedance control and backdrilling. BD requires a large BD-antipad AP= BD + 2\*drillclearance. The drill clearance is usually 5...8mil on each side, depending on our fab. The BD tool size is usually 6...12 mil larger in diameter than the via drill size, also depending on the fab. So, we need to create two rules under CM> AllR> Plane> Plane Cl, one for all signals with 5mil clearance, and one for the net or DP classes that belong to 8Gig+ SERDES difffpairs to force a large AP. Clearance= (AP-viadrill)/2. Signal layers also need a route keepout circle the same size as the BD antipad on planes.

Dual-<u>voids</u> are required for high-speed diffpairs on plane layers. Select GND layer on bottom tabs, then Place> Arc(center) on the

pins then Place> Fill between. Either a small rectangle and 2 arcs, or a large rectangle to envelop them. If the clearance rule-driven void is large enough then we don't need extra arcs. We copy these on all planes. We can also copy this to the route keepouts, to help backdrilling and prevent signals passing between p/n vias.

<u>DRC</u> check: Tools> Design Rule Check. The list of DRC violations should be worked down to zero by interactive layout editing, except a few items that are reviewed and accepted/waived.

<u>**Thieving**</u> cannot be applied in Altium, but we could use polygon pours with crosshatched pattern or rely on our PCB fab.

Preparing for <u>manufacturing</u>: Every layer should have text outside of the outline about layer name, layer number, whether it is upside-down (mirrored), company info and design part numbers. On one mechanical layer meant for fab drawing, we place tables with Place> Drill Table and Place> Layer stack table, then we manually add text about technology statements, materials, surface finish, coupons, impedance and loss tables. We also create an assembly drawing on another mechanical layer, for verifying the build, by using a dimensioned DXF from our ME. Once all done we fab-out: File> Fabrication Outputs> Gerber Files, and also NC Drill. We send a 3D model to our ME, to verify system fit: File> Export> Step3D. We generate additional documents: File> Assembly> Pick & Place and Assembly drawing, and File> Smart PDF. Or all this in a more complicated way: Projects Panel> PRJPCB> rightclick> Add New> Output Job file.

We can export <u>data reports</u> from the PCB panel. Select the desired object type (xSignals, Components), then select all classes and all objects with CTRL+A, then rightclick>Report>Export.

#### 2.6. Design Reuse

Design-reuse with a project is done using multi-channel hierarchical designs, with multiple instances of the same sch sheet symbol. Each will create a "room" in the PCB, then we manually place&route one channel, then copy the work over to the other channels: Design> Rooms> Copy Room Formats. Reusing designs from other projects can also be done: File> New> Reuse Block, it will have both a schematic (single page) and a PCB file, we edit both and save, then on the Project panel "save to server". In our new project schematics Place> Reuse Block, the Design Reuse panel opens, we find out block, place button> rightclick> Place As Sheet Symbol.

# 3. High-Speed Signal Objects

The connection objects define the signals, or groups of signals. They can be browsed on the PCB panel. Categories:

- ♦<u>Net</u>: created using net labels in schema.

- ★Bus: create using bus symbols in schema, it uses indexed net names, like ABC1\_[7..0] → ABC1\_0. For serdeslinks, it is better not to use buses, unless hierarchical.

- Diffpair (DP): Create them in the CM Physical tab with rightclick > diffpair > Create Diffpairs From Nets, or in the PCB panel's "Differential Pair Rule Wizard" both objects and rules get created. Or graphically in the sch.

- Met Class (NetC): A group object. In PCB using Design> Classes window (add new). Used for all same type (non-DP) signals on a bus, for length rules. Also used on trace width (impedance) rules for single-ended.

- Diffpair Class (DPC): Similar to net class, create in the PCB Design>Classes editor. We need two rules for our DP class: a width and a diffpair rule (phase tol, gap, uncoupled). We need one for lane-to-lane matching.

- **♦ <u>From-To</u>**: Same as the Allegro PinPair, but obsolete.

- **xSignal** (XS): Same as the Allegro PinPair, preferred. This is to control propagation delay from a pin to another pin. On a DDR4 fly-by address bus, on every address net we would have an xSignal from CPU-DRAM0, another

from CPU-DRAM1... They should be created with Design> xSignals> Create xSignals, or with a wizard. Xsignals also connect nets through res/cap.

- \*xSignal Class (XSC): Similar to a matched group of PinPairs in Allegro. We create one XSC for all the xSignals of all DDR4 address nets between CPU-DRAM1. Then create a length matching constraint/rule for that XSC. Another XSC and a rule for CPU-DRAM2.

- XNET: They can be created in the CM, XNETs are for two nets passing a series passive part.

<u>Classes</u> are used to group signals before adding them to a rule. We can have net classes, DP classes, xSignal classes. Classes are created in the "Object Class Explorer" at Design>Classes, by selecting a category, rightclick> Add Class, then add items to it. Diffpairs should be put into DP classes only, not net classes, to avoid double definition of width when using the CM (not DRE).

Trace **length measurement** still has bugs in AD25. It might fail to measure xSignal lengths accurately, which case we have to delete and reroute it. Either little trace segments overlap with others, or a segment is not counted at all.

<u>Xsignals and xSignal classes</u>, as well as their associated design rules could be created through the xSignal wizard: <u>Design></u> xSignals> Run Xsignals Wizard. The other way is through <u>Design> xSignals> Create xSignals</u> (select source, load, nets, then analyze, OK, redo for the next lane or chip), which better shows exact parts. The XS names will end with "\_PP1...N", where N is the Nth chip on the bus. A third way is in the CM>Electrical>Nets tab, click on any nets, then the Topology columns, then in the drop-down select "custom". In the <u>Design></u> Classes> xSignal Classes we have to create XSCs so we can apply rules to them later in the CM. Use the search with "\*" to get for example "MEM0\_A\*PP1" for address at DRAM1. We create XS for point to point buses also, so we can match them in XSCs.

|                                                                                                                                                                                                                            | Create xS                                   | ignals Betwee                                                                                            | n Components                                                                                        |                                                                                                                                                                                                   | ×          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <filter components<="" source="" td=""><td></td><td></td><td></td><td></td><td></td></filter>                                                                                                                              |                                             |                                                                                                          |                                                                                                     |                                                                                                                                                                                                   |            |

| Source Component (1 selec<br>R26 - 6-1622826-4<br>U1 - XCKU060-2FFVA1517E<br>U2 - XCKU060-2FFVA1517E<br>U3 - A09508BCPZ                                                                                                    | ted)                                        | <u> </u>                                                                                                 | Destination Cor<br>R19 - 6-1622826<br>R20 - 6-1622826<br>R21 - 6-1622826<br>R22 - 6-1622826         | 5-4<br>5-4                                                                                                                                                                                        | <u>^</u> ^ |

| US - AD95066CP2<br>U4 - MT40A2G8AG-062E_AI<br>U5 - MT40A2G8AG-062E_AI<br><filter nets="" source=""></filter>                                                                                                               |                                             | Nets                                                                                                     | R22 - 6-1622020<br>R23 - 6-1622820<br>R24 - 6-1622820<br>R25 - 6-1622820<br>R26 - 6-1622820         | 5-4<br>5-4<br>5-4                                                                                                                                                                                 |            |

| Source Component Nets (2<br>MEM0_APAR<br>MEM0_CK_N<br>MEM0_CK_P<br>MEM0_DQ0<br>MEM0_DQ1                                                                                                                                    | 5 selected)                                 |                                                                                                          | U2 - XCKU060-2<br>U3 - AD9508BC<br>U4 - MT40A2G8<br>U5 - MT40A2G8<br>U6 - MT40A2G8<br>U7 - MT40A2G8 | PZ<br>AG-062E_AIT:F<br>AG-062E_AIT:F<br>AG-062E_AIT:F                                                                                                                                             | ļ          |

| <ul> <li>xSignals (104 selected)</li> <li>Name</li> <li>MEM0_ABA0_PP1</li> <li>MEM0_ABA0_PP2</li> <li>MEM0_ABA0_PP3</li> <li>MEM0_ABA0_PP4</li> <li>MEM0_ABA1_PP1</li> <li>MEM0_ABA1_PP3</li> <li>MEM0_ABA1_PP3</li> </ul> | Nodes 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | Source<br>U1.E31 (ME<br>U1.E31 (ME<br>U1.E31 (ME<br>U1.E31 (ME<br>U1.D31 (ME<br>U1.D31 (ME<br>U1.D31 (ME | MO_ABA0)<br>MO_ABA0)<br>MO_ABA0)<br>EMO_ABA1)<br>EMO_ABA1)                                          | Destination<br>U7.K2 (MEM0_ABA0) + 25<br>U6.K2 (MEM0_ABA0) + 25<br>U5.K2 (MEM0_ABA0) + 25<br>U4.K2 (MEM0_ABA0) + 25<br>U7.K8 (MEM0_ABA1) + 25<br>U6.K8 (MEM0_ABA1) + 25<br>U5.K8 (MEM0_ABA1) + 25 |            |

| Include created xSignals into                                                                                                                                                                                              | o class: All xSig                           |                                                                                                          |                                                                                                     |                                                                                                                                                                                                   | -          |

| xSignals in list : 104                                                                                                                                                                                                     |                                             |                                                                                                          | Analyz                                                                                              | е 🔻 ОК                                                                                                                                                                                            | Cancel     |

| Members<br>M0_D0*PP1 <b>2</b><br>10_D00*MEM0_ADDR0_PP1       | Members<br>*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10_DQ0_PP1 <2 3<br>10_DQ1-MEM0_ADDR1_PP1                     | »                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10_DQ1_PP1<br>10_DQ2-MEM0_ADDR2_PP1<br>10_DQ2_PP1            | ,,<,⊐4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10_DQ3-MEM0_ADDR3_PP1<br>10_DQ3_PP1<br>10_DQ4-MEM0_ADDR4_PP1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10_DQ5-MEM0_ADDR5_PP1<br>10_DQ5_PP1                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10_DQ6_PP1<br>10_DQ7-MEM0_ADDR7_PP1                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                              | 00 DOL 1991<br>00 DO |

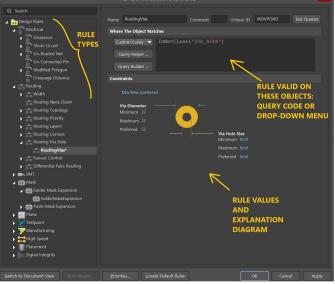

## 4. Design Rules

In Altium Designer in the traditional flow we normally specify PCB design rules in the **Design Rules editor** (DRE), in the **Design> Rules...** menu item, instead of using a constraint manager. For a PCB design, we have to set up various general design rules, PCB fabricator-driven rules, as well as high-speed design related trace length and impedance-driven width rules. In every category there is a default rule, and several user created ones that only apply to specific objects.

When the **PRJPCB is created** we have to decide whether we will be using the legacy design rules in the design rules editor (DRE), or the constraints manager (CM).

The DRE has a <u>tree structure</u>. Each item in the left menu is a rule category. We can create several new rules for each category, each rule will be applied to one class (or complex formula), by rightclick> New Rule. Important categories:

- Elecrical> clearance> clearance: mfr spacing.

- Routing> width>width: trace width.

- Routing> rout.via style: Set diameter, drill size, tenting.

- Routing> Differential: diffp gap, phase-tol and uncoupled.

- Mask: solder mask and paste mask expansion param. Create a rule for vias with scope="IsVia", and set tenting on top and bottom. The default rule for all other pads should be 2mil expansion and no tenting.

- ◆Plane: power plane/shape param, and via conn style.

- High speed> Matched net lengths: Matching rules are for setup/hold timing on source-synchronous and clockforwarding buses.

High speed> Length: max total trace length rules are for synchronous or asynchronous bus SU/H timing or for SERDES link loss budget (dB/inch).

There is always a **<u>default</u>** rule, and specific rules for defined objects (nets, classes). The default rules are based on fabricator minimum sizes (capability), the specific ones on calculations.

The typical **<u>DRE flow flow</u>**: 1. On PCB panel create objects like diffpairs, 2. In design>Classes create classes, 3. In Design Rules create rules that apply to classes.

Every board needs **basic rules** like via direct plane connect and plane clearance under DRE>Plane, component-to-comp clearance under DRE> Placement, default trace width under DRE> Routing> Width and Via Style (size), and DRE> Electrical> Clearance for copper trace gaps enforced by DRC and interactive push routing. Mask> SolderMask typically 2-3mils depending on fab, and Routing> Fanout Control for via patterns.

We can specify PCB design <u>rules in the schematics</u> level as well. We add one PCB\_Layout directive (which can contain multiple rules) to a net. Instead of specifying the object to apply in the rule, the object is specified graphically by attaching the rule symbol to net or to multiple nets (copies of the same directive). We can place a rule directive from the Place> Directives> Parameter Set, then doubleclick on the symbol and doubleclick on the rule in the list, then click on the "Edit rule Values" button.

<u>Trace width</u>: Normally we put a group of nets based on characteristic impedance into a Net Class (for single-ended) or DP class. Then we set up a DRE> Routing> Width rule for every class separately, and also a default width rule for all other or non-impedance controlled traces (4mil). There are 3 values: for the default rule set min=pref<<max, for others min=pref=max. We should use width rules instead of impedance rules, from our fab vendor's impedance/width/space calculations (from the negotiated approved stackup document).

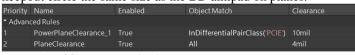

**Spacing** in PCB design has two aspects: manufacturability and controlling crosstalk levels. For the first aspect, we set up a DRE> Electrical> Clearance rule, which is normally the minimum spacing that our PCB manufacturer recommends. The Differential Pair rules also contain a field called "Gap", but this is a related to the differential impedance of the diffpair. For crosstalk control we use a more flexible spacing rule: DRE> High-Speed> Parallel Segment rule in the Design Rule Editor. This rule ignores short parallel segments, and only checks spacing if the two traces run too long in parallel. Basic spacing is enforced by a push/shove force in interactive routing. Sometimes we want to specify spacing (Parallel Segmenth rule) between differential pairs within a group, so we specify the rule's scope like "InDifferentialPairClass('classname')" for the first object and "IsDifferentialPair" for the second object.

For <u>diffpairs</u> the DRE> Routing> Differential Pair Routing rule has to be set up for every Differential-Pair Class, or to a list of classes. The rule specifies the trace spacing (Gap) between the positive and negative trace within a diffpair, and it is enforced in interactive editing when we use the Interactive Differential Pair routing option. Diffpair impedance is based on width+gap, we set the gap in the diffpair rule and the width in the width rule. We will also have to set up two "Matched Net Lengths" rules applied to a DP class, one to meet the phase tolerance requirements (within DP=On, others=Off), and another one for lane-to-lane matching (within DP=Off, others=On). If we have two multi-lane PCIe links, then each will be in a different DP class. <u>Matched length</u>: With this rule we can control the trace lengths relative to each other in a class of signals, diffpairs or xSignals. It is used on source synchronous buses like DDR4 data bus, for diffpair phase tolerance matching or for diffpair lane-to-lane matching. We can find this at DRE> High Speed > Matched Net Lengths. An important parameter of the rule is the types of objects which between the rule will be applied. For differential phase tolerance rules, we enable only the "Check Nets Within Differential Pair" option, and leave the other two options disabled. For lane-to-lane matching or for single-ended buses we enable the opposite. Note that the "Tolerance" value in the rule is the maximum difference between the longest and shortest track.

Min/Max trace length: With this rule, we can specify a length range for a class of signals (Net/DP/XS). We can find the DRE> High Speed > Length rule in the Design Rules Editor. It is useful for synchronous, asynchronous and loss budget driven buses.

## 5. Constraint Manager

Starting from 2024 Altium supports a spreadsheet-like constraints manager window, like Cadence Allegro and Mentor Expedition has. Open: Design > Constraint Manager. This is not available in the cheapest license option. This is preferred instead of using the DRE if we have hundreds of xSignals or diffpairs, on large server or router board designs. When a project starts we have to decide whether it will be a legacy design rules-based design or a CM based design, we cannot have both. Although we can still migrate an existing design from DRE to CM: Design > Migrate Project to Constraint Manager Flow. Migration only works if the system feature is enabled in: Tools> Preferences> System> General> Advanced> Constraint Manager. Project Migration Wizard = 1, then restart Altium.

The contents of CM are saved into an <u>XML file</u>, but only when we close Altium. There is a bug in AD25, so we cannot enter values to xSignal classes like tolerance or Target, but there is a solution: Once we set up all xSignals and XSCs, save, close Altium, then open Altium again, go to CM and enter these values, save, close Altium (to ensure it doesn't crash and lose all constraints, and reopen again). Now the constraints are usable in editing and DRC.

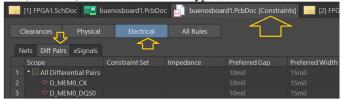

It has <u>3 tabs</u>: Clearances, Physical (width, diffpairs), Electrical (lengths). Under electrical, there are 3 sub tabs: Nets, Diffpairs, and xSignals. In any of these we can also create classes, by selecting multiple signals, rightclick>classes>... or create new objects like DP, XS, XSC... The Clearances tab allows us to add new rules, the Phys/Elec tabs list objects that we can enter numbers for. The last tab (AllRules) shows a tree of rule types, similar to the old DRE.

We can use <u>Constraint sets</u>: Once we set up parameters for one object, we can rightclick > Save As Constraint Set, then we can reapply it to other objects: rightclick> Select Constraint Set.

In the <u>Clearances tab</u> we can define a clearance between Net/DP classes in a matrix. We have to add existing classes to the matrix. When we click [+Add] then it creates both a column+row.

| Clearances          | Physical   | Electrical | All Rules |                   |

|---------------------|------------|------------|-----------|-------------------|

|                     | 🖻 All Nets | S CLKPC    | CIE 🗦 MC  | oq_width 🛛 😂 Pcie |

| 1 🖻 All Nets        | 4mil       |            |           |                   |

| 2 🍣 CLKPCIE         | 4mil       | 4mil       |           |                   |

| 3 ∋ MDQ_WI          | DTH 4mil   | 4mil       | 4mil      |                   |

| 4 <sup>©</sup> PCIE | 4mil       | 4mil       | 4mil      | 4mil              |

In the **Physical tab** we can see most signal objects types in a tree hierarchy browser view, like Class/DP/nets, and specify trace width and via style/size to them. The PolygonConnect column should be set "DirectConnect" for "IsVia". We can auto create all diffpairs here: rightclick > diffpair > Create Diffpair From Nets. The editor will find them all from name suffixes \_P/\_N.

|                        | Constraint Set | Min Width | Preferred Width | Preferred Diff Pair Gap |      | Via Style   |

|------------------------|----------------|-----------|-----------------|-------------------------|------|-------------|

| All Nets               |                | 4mil      | 4mil            | 10mil                   | 4mil | 20mil, 8mi  |

| All Differential Pairs | DP CLASS       | 4mil      | 5mil            | 6mil                    |      | 201111,0111 |

| • S CLKPCIE            |                | 4mil      | 4mil            | 6mil                    | 4mil |             |

| • O REFCLK PCIED -     | DP             |           |                 |                         |      |             |

| ≈ REFCLK_PCIE0_N       | 1 🔍            |           |                 |                         |      |             |

| REFCLK_PCIE0_P         | NETS           |           |                 |                         |      |             |

| D_REFCLK_PCIE1         |                |           |                 |                         |      |             |

| ≈ REFCLK_PCIE1_N       |                |           |                 |                         |      |             |

| ≈ REFCLK_PCIE1_F       |                |           |                 |                         |      |             |

| MEMCLK                 |                | 4.8mil    | 4.8mil          | 5mil                    |      |             |

In the **Electrical tab** we can view/edit trace length related rules. We enter values into an existing table, instead of creating rules. The Electrical tab has three different sub-tabs: Nets, DP and xSignals. Each shows object types in a hierarchy/tree browser. On the Nets sub-tab, we can create XNETs, and we can enter numbers for max total length (for synchronous buses and loss-driven SERDES links) and max via stub length constraints (for 8G+SERDES links). On the Diffpairs sub-tab we can define diffpairs, and we can enter numbers for diffpair width, gap, uncoupled length and phase tolerance of the diffpairs.

The <u>xSignals sub-tab</u> at CM> Electr> xSignals tab doesn't allow object creation, so we have to do that in the Design> xSignals> Create xSignals menu. When we first create XS/XSC objects, the CM> Electr> xSignals tab seems to be read-only, so we have to save, close Altium, reload Altium, and open CM, now we can enter values. XSC-based rules in Altium were made for trace length matching rules, so we have to enter tolerance in +/-5mils or something, and click Target and open a drop-down menu to select which member of the XSC will serve as a target length for all other members. If we need max length rules on xSignals, like on a synchronous multi-master PCI bus, then we have to use the AllRules tab instead of the Electr> xSignals tab. The CM will display the length measurements for each object as "Actual Value", or the matching rule deviation as "Margin". The PCB panel also displays these measurements.

| [1] FPGA1.SchDoc      |                |                 | osboard1.PcbDoc [Constrai | nts] * 삼 Horr | ne Page 🛛 📻 [2] FPGA2. |

|-----------------------|----------------|-----------------|---------------------------|---------------|------------------------|

| Clearances Phy        | rsical Electri | cal All Rules   |                           |               |                        |

| Nets Diff Pairs xSigr |                | >               |                           |               |                        |

| Scope                 |                |                 | Matching Target           | Actual Value  |                        |

| 1 • 🖾 All xSignals    | □ 1            | -               | -                         | -             | -                      |

| 2 • 7 MADD_0          | 2              | Enter tolerance | Not Defined               |               |                        |

| 3 * AMADD_1           |                | Enter tolerance | Not Defined               |               |                        |

| 4 • A MADD 2          |                | Enter tolerance | Not Defined               |               | <b>Readouts from</b>   |

| 5 • 🖆 MADD 3          |                | Enter tolerance | Not Defined               |               |                        |

| 6 · 7 MD_0            |                | Enter tolerance | Not Defined               | -             | routed traces          |

| 7 • 🖓 MD 1            | -xsc           |                 | Not Defined               |               |                        |

| 8 * # MD_2            |                |                 | MEM0_DQS2_P_PP1           | 6             |                        |

| 9 ST MEM0_DQ16        | 5_PP1          |                 |                           |               | -94.991mil             |

| 10 ST MEM0_DQ17       | 7_PP1 / XS     |                 |                           |               | +36.0787mil            |

| 11 J MEM0_DQ18        | 3_PP1          |                 |                           |               | -27.9661mil            |

| 12 S MEM0_DQ19        | PP1            |                 |                           |               |                        |

| 13 S MEM0_DQ20        | )_PP1          |                 |                           |               |                        |

| 14 S MEM0_DQ21        | _PP1           |                 |                           |               |                        |

| 15 S MEM0_DQ22        | 2_PP1          |                 |                           |               |                        |

| 16 S MEM0_DQ23        | 3_PP1          |                 |                           |               |                        |

| 17 ST MEMO_DQS2       | 2_N_PP1        |                 |                           |               |                        |

| 18 S MEM0_DQS2        | 2_P_PP1        |                 |                           |               |                        |

| 19 • 🕫 MD_3           | 3              | 1000mil         |                           |               |                        |

|                       |                |                 | Not Defined               |               |                        |

|                       |                | 11              | MEM0_DQ31_PP1             |               |                        |

|                       |                | 4               | MEM0_DQS3_P_PP1           |               |                        |

|                       |                | 20 <b>-1</b> 1  |                           |               |                        |

|                       |                |                 | MEM0_DQS3_N_PP1           |               |                        |

The AllRules tab: This shows a tree of many rule types, similar to the old DRE, mainly for basic rules. Check the DRE section for detailed explanations! Here we can create new rules by rightclick> Add Custom Rule, then enter ObjectMatch ([...]> Open Query Builder for classes or object types) and numbers. In the CM>AllRules > Mask> SolderMask category create a rule for vias with scope="IsVia", and set tenting on top and bottom. The default rule for all other pads should be 2mil expansion and no tenting. CM>AllRules > Routing> Routing Via Style sets the via pad and drill diameters. CM> AllRules > Routing> Fanout Contr sets pattern (auto, out, away, centered). The plane via connection style (DirectConn), and plane layer clearance have to be set in CM> AllRules> Plane> Power Plane Connect Style, and clearance. The plane clearance should be set to achieve a desired antipad size AP=BD+12mil= drill+2\*CL. The CM> AllRules> HighSpeed> Parallel Segment is good for crosstalk control spacing that is only checked if it runs long (past limit). If we need max length rules on xSignals, like on a synchronous multi-master PCI bus, se set up a rule under CM> AllRules> HighSpeed> Length. A multi-lane differential SERDES link requires lane-tolane matching, with the CM> AllRules > HighSp> Matched Length. Backdrilling is defined by max stub length and oversize (each side of hole) in CM> AllRules> HighSpeed> BackDrilling. BD also requires definitions in the Layer Stack Manager. Placement spacing: CM> AllRules > Placem> CompClearance.

| Clearances                     | Physical                                                      | Electrical | All Rules |              |                         |         |                         |         |         |

|--------------------------------|---------------------------------------------------------------|------------|-----------|--------------|-------------------------|---------|-------------------------|---------|---------|

|                                |                                                               |            |           | Priority     | Name                    | Enabled | Object Match            |         | Maximur |

| <ul> <li>Electrical</li> </ul> |                                                               |            |           |              | iced Rules              |         |                         |         |         |

|                                | ircuit (1)<br>ted Net (1)<br>inected Pin (0)<br>d Polygon (1) |            |           | 1<br>• Basic | MaxMinLength_1<br>Rules | True    | InxSignalClass(MADD_07) | 2000mil | 6000mil |

| Creepage<br>High Speed         |                                                               |            |           |              |                         |         |                         |         |         |

|                                |                                                               |            |           |              |                         |         |                         |         |         |

|                                |                                                               |            |           |              |                         |         |                         |         |         |

| Matche                         | d Lengths (14)                                                |            |           |              |                         |         |                         |         |         |

For <u>diffpairs</u> in the DRE we specify 4 rules, a width, a diffpair rule, a matching rule for tolerance and a matching rule between lanes. In the CM we enter values for diffpairs on the CM> Electr> Diffp sub-tab, and on the CM> AllRules> HighSp> Matched Length sub-tab also for lane matching (rightclick> add custom rule, Object= InDifferentialPairClass('NAME'), then select "group- matched"). Altium25 seems to define width and gap rules in two places, so to avoid using the wrong values in routing, we should set the same at both: CM> Physical and at CM> Electr> Diffp. Most values are entered to the rows of the DPCs. If we have two multi-lane PCIe links, then each will be in a different DPC.

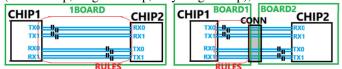

Maximum Length constraint values for SERDES buses come from insertion loss budget calculations. The dB/inch loss data, specific to a fabricator and material combination, comes from VNA measurements on Delta-L test boards, then the max trace length is calculated as L<br/>budget/dBpi. The total budget comes from the relevant standards like IEEE802.3xx, or SFF8418. For synchronous, asynchronous, source-synch and clock forwarding buses the rule values are either obtained from the chip vendor's datasheet or design guide document, or we calculate them using a pre-layout timing analysis calculator spreadsheet, like this one: https://www.buenos.extra.hu/iromanyok/PCB Timing analysis.xls

| I prearing in opeea |            |                            |

|---------------------|------------|----------------------------|

| Case                | Objects to | Constraint numbers entered |

|                     | create     | in CM                      |

|                                 | 1          |                                                       |

|---------------------------------|------------|-------------------------------------------------------|

| Differential Pair point-        | •DP        | • CM> Physical (DPC)                                  |

| to-point signal                 | •DPC       | • CM> Electr> Diffp (DPC)                             |

| IC 1 IC 2                       |            | <ul> <li>CM&gt; AllRules&gt; HighSpeed&gt;</li> </ul> |

|                                 |            | Parallel Segment. (DPC)                               |

|                                 |            | • CM> AllRules> HighSpeed>                            |

|                                 |            | BackDrilling (DPC, if >8Gbps)                         |

| Single-ended Sync/              | •NetC      | • CM> Physical (NetC)                                 |

| Async point-to-point            | ·Neic      |                                                       |

| bus with min/max len.           |            | • CM> AllRules> HighSpeed>                            |

| bus with him/max len.           |            | Length (NetC)                                         |

| IC 1 NET A IC 2                 |            | • CM> AllRules> HighSpeed>                            |

| NET_B                           |            | Parallel Segment. (NetC)                              |

|                                 |            |                                                       |

| Single-en Source-sync           | •NetC      | • CM> Physical (NetC)                                 |

| point-to-point bus              | •XS        | • CM> Electr>xSignals (XSC)                           |

| with matched lengths            | •XSC       | <ul> <li>CM&gt; AllRules&gt; HighSpeed&gt;</li> </ul> |

| IC 1 NET A IC 2                 |            | Parallel Segment. (NetC)                              |

| NET_B                           |            |                                                       |

|                                 |            |                                                       |

| Multi-lane Point-to-            | •DP        | • CM> Physical (DPC)                                  |

| point diff SERDES               | •DPC       | • CM> Electr> Diffp (DPC)                             |

| bus                             |            | <ul> <li>CM&gt; AllRules&gt; HighSp&gt;</li> </ul>    |

| IC 1 IC 2                       |            | Matched Length (DPC)                                  |

| DP_B                            |            | <ul> <li>CM&gt; AllRules&gt; HighSpeed&gt;</li> </ul> |

|                                 |            | Parallel Segment. (DPC)                               |

|                                 |            | • CM> AllRules> HighSpeed>                            |

|                                 |            | BackDrilling (DPC, if >8Gbps)                         |

| Single-ended Sync/              | •NetC      | • CM> Physical (NetC)                                 |

| Async multi-drop bus            | •XS        | • CM> AllRules> HighSpeed>                            |

| with min/max length.            | •XSC       | Length (XSC)                                          |

|                                 |            |                                                       |

|                                 | (one/chip) | • CM> AllRules> HighSpeed>                            |

| A<br>NET A B C D                |            | Parallel Segment. (NetC)                              |

| NET B                           |            |                                                       |

| Single-ended Source-            | •NetC      | • CM> Physical (NetC)                                 |

| sync multi drop bus             | •XS        | • CM> Electr>xSignals (XSC)                           |

| with matched lengths            | •XSC       | • CM> AllRules> HighSpeed>                            |

| IC 1 IC 2 IC 3                  | (one/chip) | Parallel Segment. (NetC)                              |

|                                 | (one emp)  | aranei Segment. (INCLC)                               |

| A<br>NET A B C D                |            |                                                       |

| NET B                           |            |                                                       |

| Diff multi drop bus             | •DP        | • CM> Physical (DPC)                                  |

| (like DDR4 clock)               | •DPC       | • CM> Electr> Diffp (DPC)                             |

| IC 1 IC 2 IC 3                  | •XS        | • CM> Electr>xSignals (XSC)                           |